Adding Yamaha YM2612 support has begun

So after much time talking about it, and doing research, I’ve finally got around to spending some time on adding Yamaha YM2612 support to the badge computer.

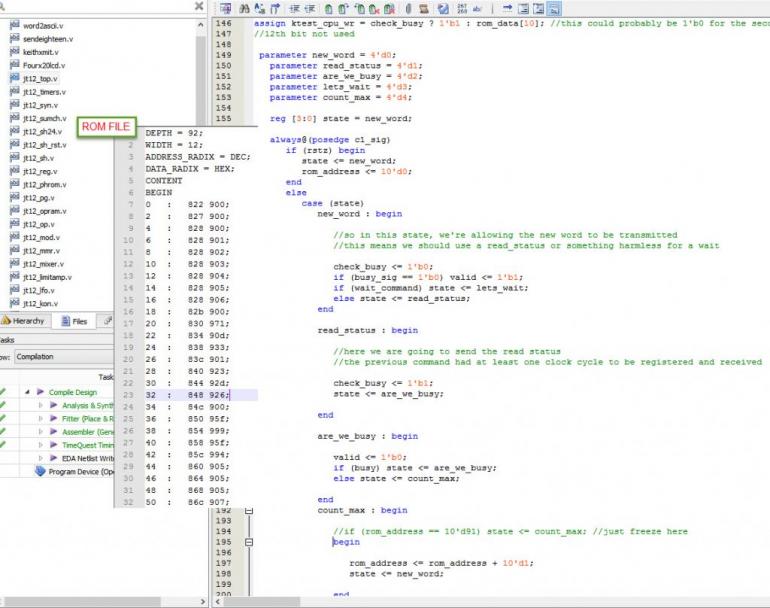

I created a small verilog driver that read the contents of rom that contained essentially VGM instructions to both initialize the JT12 chip and play a single, what I believe to be Middle C note, on a grand piano. The verilog is mostly a state machine that reads from the rom, sends the command, sends a read status command, waits for a chip to become ready, and then bumps the address inside the ROM file to grab the next command. I also implement a simple wait 1 second command because a pause between KEY DOWN and KEY UP.

I used a sample YM2612 program from here : http://www.smspower.org/maxim/Documents/YM2612. Scroll all the way down.

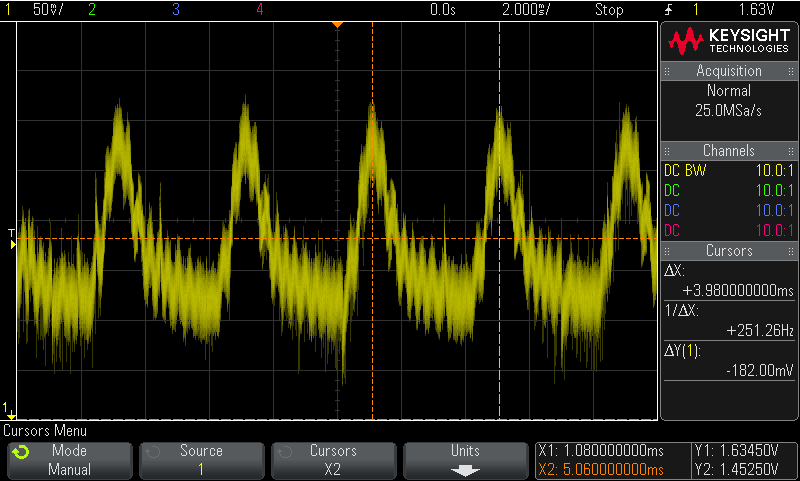

I created a simple low-pass filter using a capacitor and a resistor because the audio was complete trash from the FPGA. It’s still not perfect, but since the final output will be controlled through my external DAC, I’m not worried about optimizing it for now.

After some tweaking of my o’scope I finally got some reasonable looking sine wave output, where I can identify the center frequency of about 251.26hz. Middle C is a little bit higher at 261hz, but there are a ton of variables here — this isn’t a pure sine wave output.

My plan is to write a VGM player, or similar, in 68000 assembly. There are some hurdles to overcome before then, because we currently have no concept of a file, file system, or any real permanent storage beyond FLASH ROM space, which is very limited. I’d like to add sdcard support, but I have much I want to accomplish over the next two months in preparation for the HOPE 2018 conference.