Articles from Techtravels Amiga Blog

Primary tabs

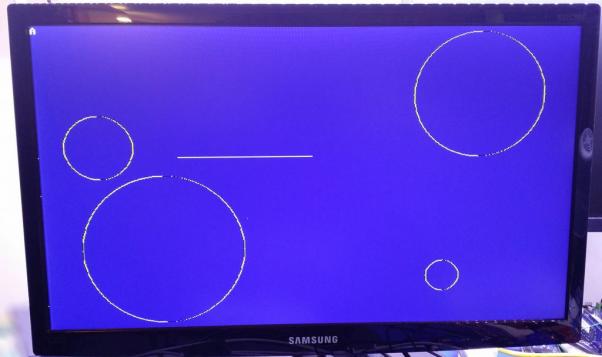

Frame Buffer and Text Generation now working…

Now that I have the 4MB SRAM board installed, I now have a frame buffer that can keep up with the video bandwidth rate.

The resolution and color depth is currently 800 x 480 x 12-bit. The computing shield I’m using only supports 12-bits, but my LCD can do 24-bit.

Essentially how my frame buffer works is that you write the 12-bit color value into an address in memory that corresponds to a location on the screen.

J68 can now speak with BEMICRO MAX 10 onboard SDRAM

So for the longest time, I’ve wanted to use the onboard 8MB SDRAM that is present on the BEMICRO MAX 10 fpga eval board. This is now a reality!

I’ve successfully integrated a controller with some glue logic to connect to the J68.

I’ve mapped the $20000-$81FFFE to the SDRAM. All calls to ROM (stored on-FPGA FLASH) are retrieved properly, some low level RAM calls access the on-FPGA M9K memory blocks, and the UARTs are all handled fairly seemlessly.

Here’s the very simple 68K memory check routine. Obviously this can be expanded on, but it’s passing!!